17.02.2026Quantum Computing

Scalable diamond Quantum Computing with cryogenic chip integration

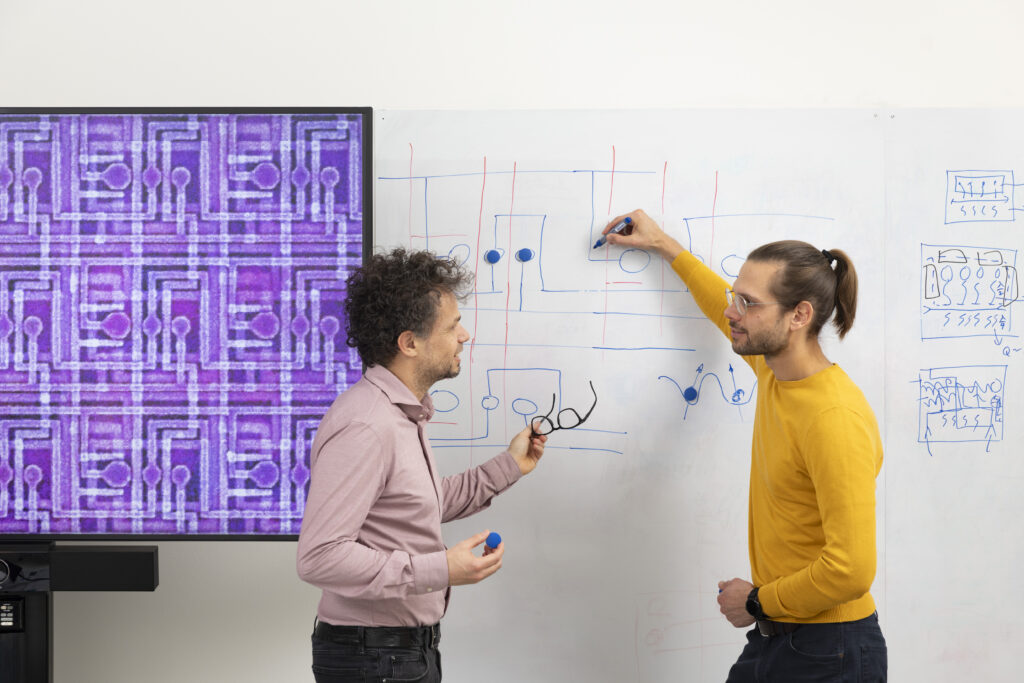

Researchers from QuTech, in a Fujitsu-funded project, have demonstrated the first cryogenic control chip capable of directly managing both electron and nuclear spins in diamond-based qubits. The innovation, which integrates a cryo-CMOS system-on-chip with nitrogen-vacancy (NV) centers in diamond, represents a significant step toward building scalable, high-fidelity quantum computers with diamond qubits. The results are presented at ISSCC in February 2026.

NV centers are among the most promising qubit platforms, combining fast electron-spin control with exceptionally stable nuclear-spin memories. However, until now, these systems have depended on room-temperature electronics connected by long cables to the cryogenic environment: a setup that considerably hinders scalability and reliability.

The new cryo-CMOS controller solves this challenge by bringing the electronics directly into the cold. Operating alongside the qubits at cryogenic temperatures, it can generate the precise, high-frequency signals needed for both electron and nuclear spin manipulation, whilst consuming minimal power, occupying minimal space and easing the connection to the quantum chip, thus being ready for scaling to large quantum computers.

High-fidelity quantum control

The integrated system achieved quantum gate fidelities of 99.3% for electron spins and 99.8% for nuclear spins, while maintaining coherence times exceeding 50 milliseconds: performance metrics approaching those required for fault-tolerant quantum computing.

By digitally adapting to the unique resonance frequency of each qubit, the chip eliminates the need for complex magnetic field tuning. This allows for many qubits to be controlled in parallel, a key requirement for scaling quantum hardware beyond laboratory prototypes. The chip’s digital-centric architecture also delivers precise amplitude and phase control while minimising heat generation, which is an essential feature for cryogenic systems, where cooling capacity is limited.

Toward scalable quantum hardware

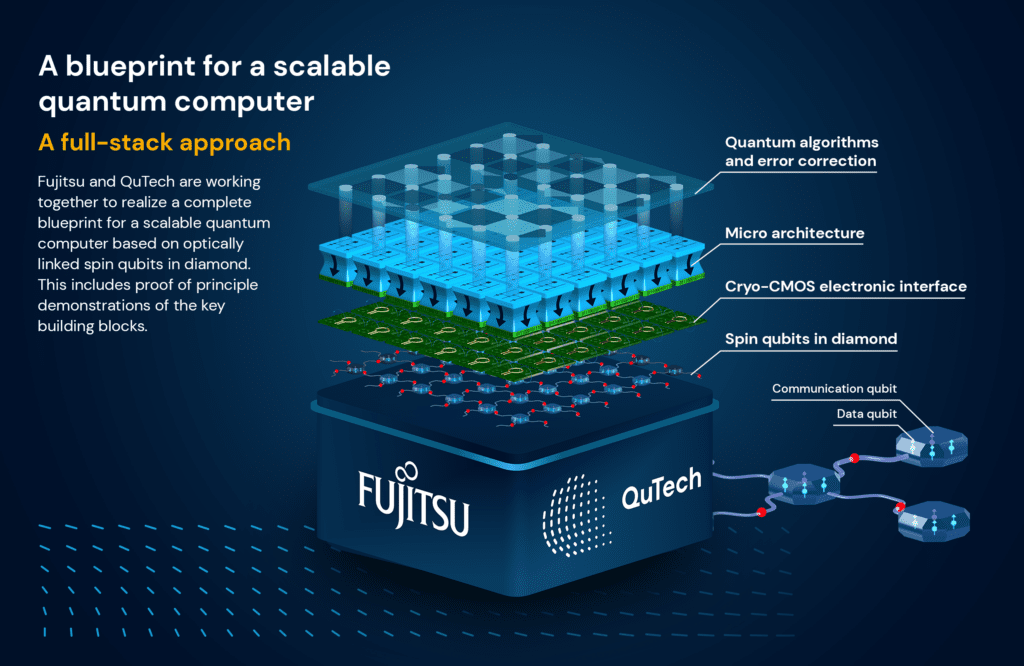

This demonstration marks a convergence of semiconductor engineering and quantum science. While the NV-center qubits remain in diamond, the cryo-CMOS controller is fabricated in a standard silicon process and operates alongside the qubits at cryogenic temperature, delivering compact, energy-efficient control where scaling typically becomes difficult. In that sense, the work is a practical step toward more tightly integrated, and eventually more manufacturable, quantum modules that combine diamond qubits with CMOS control electronics.

For Masoud Babaie, who led the development together with Fabio Sebastiano, this proves that “co-integration of color centers with cryo-CMOS as a scalable candidate for quantum computing”.

Together for a full stack quantum future

The collaboration between Fujitsu and QuTech represents a strategic industry-academia partnership aimed at building a full-stack blueprint for scalable quantum computing. With expertise from both fields, teams are developing diamond-spin qubit modules, cryogenic CMOS control electronics, and supporting optical interconnects — spanning the hardware, architecture, and algorithm layers of quantum systems.

The results of the paper will be presented at the IEEE International Solid-State Circuits Conference (ISSCC) in February 2026, regarded as the leading conference for breakthroughs in integrated circuit design. “For diamond spin qubits, the electronics can easily become the bottleneck. What we’re showing here is a concrete way to bring precise control closer to the qubits at cryogenic temperatures, without making the system more complex than it needs to be,” summarises Fabio Sebastiano. Masoud Babaie adds: “This work shows that cryogenic CMOS control can be designed to meet the stringent requirements of diamond spin qubits while remaining scalable. By tightly integrating control electronics with the qubits, we take an important step toward practical, large-scale diamond quantum processors.”