## Quantum Inspire

The number of quantum computing use cases in the realm of quantum simulations, optimization and machine learning is steadily growing. At QuTech we are convinced that offering the public broad access to technologies such as quantum computing hardware as well as a quantum computing simulator tool will further stimulate this growth. Therefore we have developed Quantum Inspire (QI), which is:

- Europe's first full-stack prototype platform for quantum computation in the cloud.

- The world's first spin-based quantum processor in the cloud.

- The world's first quantum computer in the cloud supporting multiple qubit technologies.

QI is a platform with a high degree of modularity and offers the public cloud-based access to QuTech quantum technologies such as:

- Programmable quantum processors:

- (1) SPIN-2: a 2-qubit processor based on spin qubits in Silicon, and

- (2) STARMON-5: a 5-qubit processor based on superconducting transmon qubits.

- QX-26 and QX-31: Programmable quantum computer simulator up to 31 qubits.

- Tutorials and user background knowledge on quantum information processing.

## A full-stack Quantum Computer

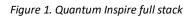

QI consists of a number of layers including quantum chip hardware, classical control electronics, a quantum compiler and a software front-end with a cloud-accessible web-interface. Such a system is called a full-stack. Full-stack systems are essential testbeds for understanding this novel computational paradigm. They can act as technology accelerators because only through careful analysis of the individual system layers and their interdependencies it becomes possible to detect the gaps and necessary next steps in the innovation roadmap and supply chain [1-3].

In its current form, programming a quantum computer is different from programming a classical computer. QI's user experience comes with a web portal (www.quantum-inspire.com) and a software development kit (SDK) to program algorithms, execute these algorithms and examine the results in various ways. QI's programming language is cQASM [4], which is developed by the Quantum & Computer Engineering group at TU Delft. Algorithms can also be programmed through third party Python-based quantum programming platforms such as ProjectQ (ETH Zurich) and QisKit (IBM), which connect to Quantum Inspire's application programming interface (API).

When executing a quantum algorithm in cQASM through the QI web-interface or API, the algorithm is routed to the chosen hardware or simulator back-end. The algorithm is compiled locally at the back-end system (Classical Processing). The compiler generates instructions for the classical control electronics (Digital Processing), which then generate the analogue control signals (Analog Processing) required to execute the algorithm on the quantum chip (Quantum Processing).

## The Quantum Processing Unit

As depicted by Figure 1. Quantum Inspire full stack, the last three layers form the QPU: the Quantum Processing Unit. The Digital and Analog Processing steps make use of both commercial electronics as well as in-house developed electronics by TNO and TU Delft, in an engineering feat that delivers the phase and amplitude modulated microwave pulses and voltage steps to execute the required qubit operations whilst synchronised at picosecond timescales [2]. Conventional DC-carrying cables and high frequency transmission lines will bring the signals to and from the quantum processor, which is kept at a temperature of 10 to 20 mK inside a dilution refrigerator. In this last Quantum Processing layer we use two different types of programmable quantum processors, both based on solid-state qubits. Solid-state qubits, in Quantum Inspire superconducting transmons and electron spins trapped in semiconductor quantum dots, are particularly promising building blocks of a quantum processor [5-10]. These devices can be manufactured and tailored by standard lithographic techniques, which is a considerable advantage for potential future large-scale integration of a large number of qubits. In addition, they are controlled and read out by current-state electronics. Superconducting transmon qubit technology is more mature at this point in time, whereas spin qubits, on the other hand, are very promising from the point of view of very large-scale integration, thanks to their small size and similarity to classical transistor technology.

Next to the two programmable quantum processors, QI supports the QX quantum computer simulator [11], which was developed by QuTech. The simulator runs both on a single node (up to 26 qubits) and on a supercomputer located on the Dutch national supercomputer at SURF in Amsterdam (up to 31 qubits) [12].

Spin-2

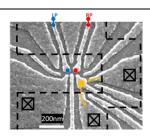

The Spin-2 QPU was developed at QuTech and consists of two single electron spin qubits hosted in a double quantum dot in isotopically purified Si-28, and allows for arbitrary singlequbit rotations and two-qubit gates. Fast readout of the quantum dot states is performed with a nearby single electron transistor. Carefully

tuned voltages applied to 14 metallic electrodes on the device, define the confinement potential for the qubit electrons and the single electron transistor. Single- and two-qubit gates are implemented by applying fast microwave and DC pulses to the same electrodes. More details on the functional requirements and the device lifecycle including materials, fabrication and electrical screening can be found in [3]. Starmon-5

The Starmon-5 QPU was developed at QuTech and consists of five superconducting transmon qubits, allowing single-qubit rotations of fixed angle and fast two-qubit gates with high fidelity. One central qubit (2) connects to each of its four neighboring qubits (0,1,3,4) via bus resonators. Each qubit has a microwave-control line for

single-qubit gates and a flux-bias line for two-qubit gates. Each qubit is independently read out using a dispersively coupled readout resonator with dedicated Purcell filter. These readout structures connect to two feedlines allowing simultaneous readout by frequency multiplexing. The nickname 'starmon' reflects the high connectivity per qubit (up to 7 ports).

| Key performance parameters      | Spin-2                   | Starmon-5                      |

|---------------------------------|--------------------------|--------------------------------|

| Material                        | Si-28 QW in SiGe         | Al, AlOx, NbTiN on Si          |

| Single qubit gate control       | EDSR microwave pulsing   | DRAG microwave pulsing         |

| Two-qubit gate control          | Exchange interaction     | Baseband flux pulsing          |

| Read-out                        | Spin-selective tunneling | Dispersively coupled resonator |

| Energy relaxation time T1       | > 20 ms (similar device) | 18 μs (average)                |

| Phase coherence time T2*        | > 6 µs                   | 23 μs (average)                |

| Single-qubit gate fidelity (RB) | ~ 99.0% (average)        | ~99.9% (average)               |

| Two-qubit gate fidelity         | Value not characterized  | ~97% (average)                 |

| Initialization+readout fidelity | ~ 85% (average)          | ~97% (average)                 |

| Single-qubit gate duration      | 250 ns (average)         | 20 ns                          |

| Two-qubit gate duration         | 150 ns                   | 60 ns                          |

| Readout duration                | 2 x 300 µs = 600 µs      | 800 ns                         |

|                                 | (sequential readout)     |                                |

## QUTECH PRESS RELEASE FACT SHEET 20 April 2020

- X. Fu, L. Riesebos, L. Lao, C. G. Almudever, F. Sebastiano, R. Versluis, E. Charbon, K. Bertels, "A Heterogeneous Quantum Computer Architecture", Proc. ACM Int. Conf. on Computing Frontiers, pp. 323–330 (ACM, 2016).

- [2] R. Versluis, "Here's a Blueprint for a Practical Quantum Computer", https://spectrum.ieee.org/computing/hardware/ here's-a-blueprint-for-apractical-quantum-computer (2020).

- [3] T. Last, N. Samkharadze, P. Eendebak, R. Versluis, X. Xue, A. Sammak, D. Brousse, K. Loh, H. Polinder, G. Scappucci, M. Veldhorst, L. M. K. Vandersypen, K. Maturová, J. Veltin, G. Alberts, "Quantum Inspire QuTech's platform for co-development and collaboration in Quantum Computing", Proc. SPIE 11324, Novel Patterning Technologies for Semiconductors, 113240J (23 March 2020.

- [4] N. Khammassi, G. G. Guerreschi, I. Ashraf and J. W. Hogaboam, C. G. Almudever, K. Bertels, "cQASM v1.0 : Towards a Common Quantum Assembly Language", arXiv :1805.09607

- [5] L. M. K. Vandersypen, H. Bluhm, J. S. Clarke, A. S. Dzurak, R. Ishihara, A. Morello, D. J. Reilly, L. R. Schreiber, M. Veldhorst, "Interfacing spin qubits in quantum dots and donors hot, dense, and coherent", NOP Quantum Information 3:34 (2017).

- [6] M. Kjaergaard, M. E. Schwartz, J. Braumüller, P. Krantz, J. I.-J. Wang, S. Gustavsson, W. D. Oliver, "Superconducting Qubits: Current State of Play", Annual Review of Condensed Matter, Physics Vol. 11 (2020).

- [7] T. F. Watson, S. G. J. Philips, E. Kawakami, D. R. Ward, P. Scarlino, M. Veldhorst, D.E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, L. M. K. Vandersypen, "A programmable two-qubit quantum processor in silicon", Nature 555, pp. 633-637 (2018).

- [8] C.C. Bultink, T.E. O'Brien, R. Vollmer, N. Muthusubramanian, M.W. Beekman, M.A. Rol, X. Fu, B. Tarasinski,

V. Ostroukh, B. Varbanov, A. Bruno, and L. DiCarlo, "Protecting quantum entanglement from qubit errors and leakage via repetitive parity measurements", Science Advances 6, eaay3050 (2020).

- M.A. Rol, F. Battistel, F.K. Malinowski, C.C. Bultink, B.M. Tarasinski, R. Vollmer, N. Haider, N. Muthusubramanian,

A. Bruno, B.M. Terhal, and L. DiCarlo, "A fast, low-leakage, high-fidelity two-qubit gate for a programmable superconducting quantum computer", Physical Review Letters 123, 120502 (2019).

- [10] R. Versluis, S. Poletto, N. Khammassi, N. Haider, D.J. Michalak, A. Bruno, K. Bertels, and L. DiCarlo, "Scalable quantum circuit and control for a superconducting surface code", Physical Review Applied 4, 034021 (2017).

- [11] N. Khammassi, I. Ashraf, X. Fu, C. G. Almudever, K. Bertels, "QX: A High-Performance Quantum Computer Simulation Platform", DATE conference, Lausanne, Switzerland, pp. 464-469 (2017),

- online: <a href="https://qutech.nl/qx-quantum-computer-simulator">https://qutech.nl/qx-quantum-computer-simulator</a>

- [12] See online: https://userinfo.surfsara.nl/systems/cartesius