# PAPER

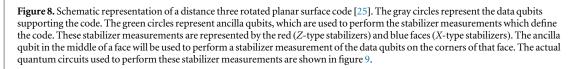

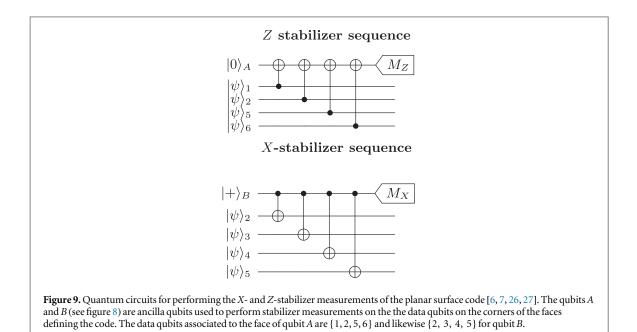

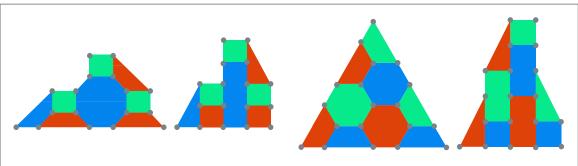

# Quantum error correction in crossbar architectures

To cite this article: Jonas Helsen et al 2018 Quantum Sci. Technol. 3 035005

View the article online for updates and enhancements.

# Quantum Science and Technology

RECEIVED 2 January 2018

REVISED 1 March 2018

ACCEPTED FOR PUBLICATION 21 March 2018

CrossMark

PUBLISHED 3 May 2018

# PAPER

# Quantum error correction in crossbar architectures

#### Jonas Helsen<sup>1</sup><sup>(1)</sup>, Mark Steudtner<sup>1,2</sup>, Menno Veldhorst<sup>1,3</sup> and Stephanie Wehner<sup>1</sup>

QuTech, Delft University of Technology, Lorentzweg 1, 2628 CJ Delft, The Netherlands

Instituut-Lorentz, Universiteit Leiden, P.O. Box 9506, 2300 RA Leiden, The Netherlands

3 Kavli Institute of Nanoscience, Delft University of Technology, P.O. Box 5046, 2600 GA Delft, The Netherlands

#### E-mail: i.helsen@tudelft.nl

Keywords: quantum computing, quantum computing architectures, control of quantum computers, quantum error correction Supplementary material for this article is available online

#### Abstract

A central challenge for the scaling of quantum computing systems is the need to control all qubits in the system without a large overhead. A solution for this problem in classical computing comes in the form of so-called crossbar architectures. Recently we made a proposal for a large-scale quantum processor (Li et al arXiv:1711.03807 (2017)) to be implemented in silicon quantum dots. This system features a crossbar control architecture which limits parallel single-qubit control, but allows the scheme to overcome control scaling issues that form a major hurdle to large-scale quantum computing systems. In this work, we develop a language that makes it possible to easily map quantum circuits to crossbar systems, taking into account their architecture and control limitations. Using this language we show how to map well known quantum error correction codes such as the planar surface and color codes in this limited control setting with only a small overhead in time. We analyze the logical error behavior of this surface code mapping for estimated experimental parameters of the crossbar system and conclude that logical error suppression to a level useful for real quantum computation is feasible.

# 1. Introduction

When attempting to build a large-scale quantum computing system a central problem, both from experimental and theoretical perspectives, is what might be called the interconnect problem. This problem, which also exists in classical computing, arises when computational units (e.g. qubits in quantum computers, transistors in classical computers) are densely packed such that there is not enough room to accommodate individual control lines to every unit. A solution to this problem, which is commonplace in classical computing systems, is a socalled 'crossbar architecture'. In this class of computing architecture we do not draw a control line to every qubit but rather organize computational units in a grid with control lines addressing full rows and columns of this grid. Control effects then happen at the intersection of column and row lines. In this way, using N control lines  $O(N^2)$  computational units can be addressed. This makes it possible to scale the system to a large number of qubits. The price to pay for this is a reduced ability to perform operations on different units in the grid in parallel. For classical systems this is not a fundamental problem, but when the computational units are qubits, whose information decays over time, parallelism becomes absolutely essential. This introduces a formidable roadblock for the development of crossbar systems for quantum computing systems. Nevertheless various crossbar architectures for quantum computers have been proposed in the past [1-5]. Recently [4] we proposed a quantum computing platform based on spin qubits in silicon quantum dots featuring a crossbar architecture. This architecture features compatibility with modern silicon manufacturing techniques and in combination with recent advances in controlling quantum dot qubits and the inherent long coherence times of spin qubits in silicon we expect it to be a formidable step forwards in creating large-scale quantum computing devices.

Any realistic quantum computing device, including the one we propose in [4], will suffer from noise processes that degrade quantum information. This noise can be combated by quantum error correction [6, 7], where quantum information is encoded redundantly in such a way that errors can be diagnosed and remedied as

they happen without disturbing the encoded information. Many quantum error correction codes have been developed over the last two decades and several of them have desirable properties such as high noise tolerance, efficient decoders and reasonable implementation overhead. Of particular note are the planar surface [8] and color codes [9], which have the nice property that they can be implemented in quantum computing systems where only nearest-neighbor two-qubit gates are available.

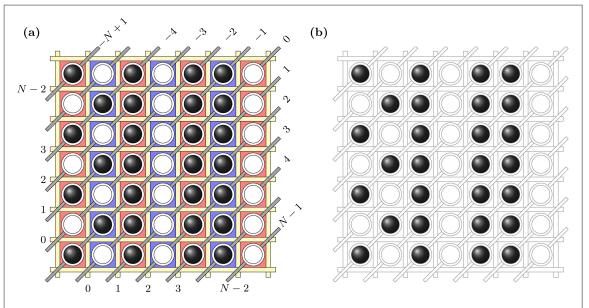

However these codes, and all other quantum error correction codes, were developed under the (often implicit) assumption that all physical qubits participating in the code can be controlled individually and in parallel. For large (read: comprising many qubits) error correction codes this introduces a tension between the needs of the error correction code and the control limitations for large systems mentioned above. While practical large-scale quantum computers most likely pose control limitations, surprisingly little work has been done in this area [10]. Here we investigate the minimal amount of parallel control resources needed for quantum error correction and focus in particular on crossbar architectures. In figures 1 and 5 we summarize the layout and control limitations of the architecture in [4]. Overcoming these limitations motivates the current work.

#### 1.1. Contributions

#### 1.1.1. Analysis of the crossbar system

We analyze the crossbar architecture we propose in [4]. We give a full description of the layout and control characteristics of the architecture in a manner accessible to non-experts in quantum dots. We develop a language for describing operations in the crossbar system. Of particular interest here are the regular patterns (see e.g. section 3.4) that are implied by the crossbar structure. These configurations provide an abstraction on which we build mappings of quantum error correction codes (see below). This analysis is particular to the system in [4] but we believe many of the considerations to hold for more general crossbar architectures.

#### 1.1.2. An efficient algorithms for control on crossbar architectures

We develop an algorithm for moving around qubits (shuttling) on crossbar architectures. We show that the task of shuttling qubits in parallel can be described using a matrix taking value in an idempotent monoid. The control algorithm then reduces to finding independent columns of this matrix, for a suitable notion of independence. This algorithm in principle allows the straightforward mapping of more complicated quantum algorithms which require long-range operations, with little operational overhead. We also expect this algorithm to be applicable to the control of more general crossbar architectures. We also sketch an algorithm for parallel two-qubit interactions in crossbar systems which produce *optimal* control sequences. This algorithm is based on computing the Schmidt-normal form of matrices with entries in the principal ideal domains  $\mathbb{Z}_2$  and  $\mathbb{Z}_4$ .

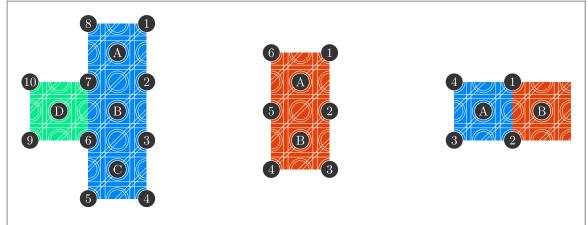

# 1.1.3. Mapping of surface and color codes

We map the planar surface code and the 6.6.6. (hexagonal) and 4.8.8. (square-octagonal) color codes [9] to the crossbar architecture, taking into account its limited ability to perform parallel quantum operations. The tools we develop for describing the mapping, in particular the configurations described in section 3.4, should be generalizable to other quantum error correction codes and general crossbar architectures.

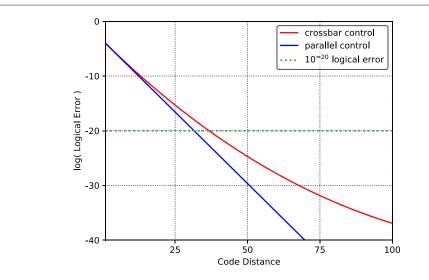

### 1.1.4. Analysis of the surface code logical error

Due to experimental limitations the mappings mentioned above might not be attainable in near term devices. Therefore we adapt the above mappings to take into account practical limitations in the architecture [4]. In this version of the mapping the length of an error correction cycle scales with the distance of the mapped code. This means the mapping does not allow for arbitrary logical error rate suppression. Therefore we analyze the behavior of the logical error rate with respect to estimated experimental error parameters and find that the logical error rate can in principle be suppressed to below  $10^{-20}$  (an error rate comparable to the error rate of classical computers [11]), allowing for practical quantum computation to take place.

Our work raises several interesting theoretical questions regarding the mapping of quantum algorithms to limited control settings, see section 6.

### 1.2. Outline

In section 2 we introduce the architecture we proposed in [4]. We forgo an explanation of the physics and focus on the abstract control aspects of the system (explaining them in a largely self-contained manner accessible to non-experts in quantum dot physics). We introduce classical helper objects such as the BOARDSTATE which will aid later developments. We discuss one- and two-qubit operations, measurements, and qubit shuttling. In section 3 we focus on parallel operations. We discuss difficulties inherent in parallel operation in a crossbar system and develop an algorithm for dealing with them efficiently. We also introduce several BOARDSTATE configurations which feature prominently in quantum error correction mappings and describe how to reach them efficiently by parallel shuttling. In section 4 we give a quick introduction to quantum error correction with a particular focus on the planar surface code and the 4.8.8. and 6.6.6. color code. In section 4.4 we bring together all previous sections and devise a mapping of the planar surface code to the crossbar architecture. This we continue in section 4.5 for the 6.6.6. and 4.8.8. color codes. Finally in section 5 we analyze in detail the logical error probability of the surface code mapping as a function of the code distance and estimated error parameters of the crossbar system.

# 2. The quantum dot processor

In this section we will give an overview of the quantum dot processor (QDP) architecture as proposed in [4]. We will use this architecture as a concrete realization of the more general idea of quantum crossbar architectures. We will focus not so much on the details of the implementation but rather focus on abstract operational properties of the system as they are relevant for our purposes. The basic organization of the ODP is that for an  $N \times N$  grid of qubits interspersed with control lines that effect operations on the qubits. The most notable feature of the QDP (and crossbar architectures in general) is the fact that any classical control signal sent to a control line will be applied simultaneously to all qubits adjacent to that control line. This means that every possible classical instruction applied to the QDP will affect O(N) qubits (these qubits will not necessarily be physically close to each other). This has important consequences for the running of quantum algorithms on the QDP (or any crossbar architecture) that must be taken into account when compiling these algorithms to hardware level instructions. Notably it places strong restrictions on performing quantum operations in parallel on the QDP. To deal with these restrictions it is important to have a good understanding of how operations are performed on the QDP. It is for this reason that we begin our study of the QDP with an examination of its control structure at the hardware level. We describe the physical layout of the system and develop nomenclature for the fundamental control operations. This nomenclature might be called the 'machine code' of the QDP. From these basic instructions we go on to construct all elementary operations that can be applied to qubits in the QDP. These are quantum operations, such as single-qubit gates, nearest-neighbor two-qubit gates and qubit measurements but also a non-quantum operation called coherent shuttling which does not affect the quantum state of the QDP qubits but changes their connectivity graph (i.e. which qubits can be entangled by two-qubit gates). All of these operations are restricted by the nature of the control architecture in a way that gives rise to interesting patterns (section 3.4) and which we will more fully examine in section 3.

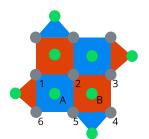

#### 2.1. Layout

A schematic overview of the QDP architecture is given in figure 1, where qubits (which are electrons, denoted by black balls) occupy an array of  $N \times N$  quantum dots (hereafter often referred to as sites). The latter are denoted by white sites when empty, since they either are occupied by a qubit or not. We will label the dots by tuples containing row and column indices  $(i, j) \in [0 : N - 1]^{\times 2}$  (beginning from the *bottom left* corner), such that a single-qubit state  $|\psi\rangle$  living on the (i, j)'th site will be denoted by  $|\psi\rangle_{(i,j)}$ . We assume the qubits to be initialized in the state  $|0\rangle$ . For future reference we note that  $|0\rangle$  corresponds to the spin-up state and  $|1\rangle$  to the spin-down state of the electron constituting the qubit.

Typically we will work in a situation where half the sites are occupied by a qubit and half the sites are empty (as seen in figure 1(a)). Because (as we discuss in section 2.3.1) the qubits can be moved around on the grid and the two-qubit gates depend on the filling of the grid, it is important to keep track of which sites contain qubits and which ones do not. This can be done efficiently in classical side-processing. To this end we introduce the BOARDSTATE object. BOARDSTATE consists of a binary  $N \times N$  matrix with a 1 in the (i, j)'th place if the (i, j)'th site contains an electron (qubit) and a 0 otherwise. The BOARDSTATE does not contain information about the qubit state  $|\psi\rangle_{(i,j)}$ , only about the electron occupation of the grid. A particular BOARDSTATE is illustrated in the left panel of figure 1.

We now turn to describing the control structures that are characteristic for this architecture. As a first feature, we would like to point out that each site is either located in a red or a blue region in figure 1 (left panel). The blue (red) columns correspond to regions of high (low) magnetic fields, which plays a role in the addressing of qubits for single-qubit gates. We will denote the set of qubits in blue columns (identified by their row and column indices) by  $\mathcal{B}$  and the set of qubits in red columns by  $\mathcal{R}$ .

Much finer groups of sites can be addressed by the control lines that run through the grid. The crossbar architecture features control lines that are connected to O(N) sites. At the intersections of these control lines individual sites and qubits can be addressed. This means that using O(N) control lines  $O(N^2)$  qubits can be controlled. As seen in figure 1 the rows and columns of the QDP are interspersed with horizontal and vertical lines (yellow), as a means to control the tunnel coupling between adjacent sites. We refer to those lines as barrier gates, or barriers for short. Each line can be controlled individually, but a pulse has an effect on all O(N) qubits adjacent to the line. Another layer of control lines is used to address the dots itself rather than the spaces in between them. The diagonal gate lines (gray), are used to regulate the dot potential. We label the horizontal and vertical lines by an integer running from 0 to N - 2 and the diagonal lines with integers running from -(N - 2) to N - 2 where the -(N - 2)'th line is the top left line and increments move towards the bottom right (see figure 1(a)). Next we describe how these control lines can be used to effect operations on the qubits occupying the QDP grid.

#### 2.2. Control and addressing

As described above, the QDP consists of quantum dots interspersed with barriers and connected by diagonal lines. For our purposes these can be thought of as abstract control knobs that apply certain operations to the qubits. In this section we will describe what type of gates operations are possible on the QDP. We will not concern ourselves with the details of parallel operation until section 3.

There are three fundamental operations on the QDP which we will call the 'grid operations'. These operations are 'lower vertical barrier' ( $\nabla$ ), 'lower horizontal barrier' (H) and 'set diagonal line' (D). The first two operations are essentially binary (on-off) but the last one (D) can be set to a value  $t \in [0: T]$  where T is a device parameter. (At the physical level this corresponds to how many clearly distinct voltages we can set the quantum dot plunger gates [4]). Although the actual pulses on those gates differ by amplitude and duration between the different gates and operations, this notation gives us a clear idea which lines are utilized. This can be done because realistically one will not interleave processes in which pulses have such different shapes. We can label the grid operations by mnemonics (which in a classical analogy we will call OPCODES) as seen in section 2.2. These OPCODES are indexed by an integer parameter that indicates which control line it applies to. We count horizontal and vertical lines starting at zero from the lower left corner of the grid (see figure 1). Note that the lines at the boundary of the grid are never addressed in our model and are thus not counted.

We indicate parallel operation of a collection of OPCODES by ampersands, e.g. D[1]&H[2]&D[5]. We also define inherently parallel versions (in section 2.2) of the basic OPCODES that take as input a binary vector V of length N (for the diagonal line this is a T-valued vector of length N)

| OPCODE  | Effect                                  |

|---------|-----------------------------------------|

| V[i]    | Lower vertical barrier at index i       |

| H[i]    | Lower horizontal barrier at index i     |

| D[i][t] | Set diagonal line at index i to value t |

OPCODE Control OPCODES Effect V[i]&D[i-j][t-1/2-k/2] (k = 1): Shuttle from (i, j) to (i, j + 1)HS[i,j,k] &D[i-j+1][t-1/2+k/2] (k = -1): Shuttle from (i, j + 1) to (i, j)(k = 1): Shuttle from (i, j) to (i + 1, j)VS[i,j,k] H[j]&D[i-j][t-1/2-k/2] &D[i-j-1][t-1/2 + k/2](k = -1): Shuttle from (i + 1, j) to (i, j)HS[i,j+1/2+k/2,-k] M[i,j,k]Measurement of qubit at (i, j) using the ancilla at (i, j + k)

Table 1. OPCODES for horizontal and vertical shuttling and measurement together with the control OPCODES required to implement these operations on the QDP.

| OPCODE | Effect                                                                                        |

|--------|-----------------------------------------------------------------------------------------------|

| V[V]   | Set vertical barrier to $V(i)$ , $\forall i \in [0: N-2]$                                     |

| H[V]   | Set horizontal barrier to $\forall$ ( <i>i</i> ), $\forall$ <i>i</i> $\in$ [0 : <i>N</i> – 2] |

| D[V]   | Set diagonal at height $\forall$ ( <i>i</i> ), $\forall$ <i>i</i> $\in$ [ $-N$ + 2: $N$ -2]   |

These grid operations can be used to induce some elementary quantum gates and operations on the qubits in the QDP. Below we describe these operations.

#### 2.3. Elementary operations

Here we give a short overview of the elementary operations available in the QDP. We will describe basic singlequbit gates, two-qubit gates, the ability to move qubits around by coherent shuttling [12] and a measurement process through Pauli Spin Blockade (PSB) [13]. All of these operations are implemented by a combination of the grid operations defined in section 2.2, and always have a dependence on the BOARDSTATE.

#### 2.3.1. Coherent qubit shuttling

An elementary operation of the QDP is the coherent qubit shuttling [12, 14], of one qubit to an adjacent, empty site. That means that an electron (qubit) is physically moved to the other dot (site) utilizing at least one diagonal line and the barrier between the two sites (see figure 2(a) for an illustration). It thereby does not play a role whether the shuttling is in horizontal (from a red to a blue column or the other way around) or vertical direction (inside the same column). However, the shuttling in between columns results in a *Z*-rotation, that must be compensated by timing operations correctly, see [4] for details. This *Z*-rotation can also by used as a local single-qubit gate, see section 2.3.3. The operation is dependent on the BOARDSTATE by the prerequisite that the site adjacent to the qubit to must be empty. Collisions of qubits are to be avoided, as those will lead to a collapse of the quantum state (see however the measurement process in section 2.3.2). We now describe the coherent shuttling as the combination of grid operations.

We lower the vertical (or horizontal) barrier in between the two sites and instigate a 'gradient' of the on-site potentials of the two dots. That is, the diagonal line of the site containing the qubit must be operated at  $t \in [0:T]$ while the line overhead the empty site must have the potential  $\hat{t} \in [0:T]$  with  $\hat{t} = t - 1$ . Note that this implies it might not be operated at all (if it is already at the right level). We will subsequently refer to the combination of a lowered barrier and such a gradient as a 'flow'. A flow will in general be into one of the four directions on the grid. We define the commands VS[i,j,k] (vertical shuttling) and HS[i,j,k] (horizontal shuttling). The command VS[i,j,k] shuttles a qubit at location (i,j) to (i + 1,j) for k = 1 (upward flow) and shuttles a qubit at location (i + 1, j) to (i, j) for k = -1 (downward flow). Similarly, the command HS[i,j,k] shuttles a qubit at location (i, j) to (i, j + 1) for k = 1 (rightward flow) and shuttles a qubit at location (i, j, j + 1) to (i, j) for k = -1 (leftward flow). See table 1 for a summary of these OPCODES.

Using only these control lines, we can individually select a single qubit to be shuttled. However, when attempting to shuttle in a parallel manner, we have to be carefully take into account the effect that the activation of several of those lines has on other locations. We will deal with this in more detail in section 3.1.

#### 2.3.2. Measurement and readout

The QDP allows for local single-qubit measurements in the computational basis  $|0\rangle$ ,  $|1\rangle$ . We can measure a qubit by attempting to shuttle it to a horizontally adjacent site that is already occupied by an ancilla qubit and then detecting whether the shuttling was successful. This process is called Pauli Spin Blockade (PSB) measurement [4, 13]. See figure 2(b) for an illustration. However, the QDP's ability to perform this type of qubit measurements is limited by three factors.

Firstly, the measurement requires an ancilla qubit horizontally adjacent to the qubit to be measured. This ancilla qubit must be in a known computational basis state. Moreover, if the ancilla qubit is in the state  $|0\rangle$  the ancilla qubit must be in the set  $\mathcal{B}$  (blue columns in figure 1) while the qubit to be measured must be in the set  $\mathcal{R}$  (red columns in figure 1). On the other hand, if the ancilla qubit is in the state  $|1\rangle$  the ancilla qubit must be in the set  $\mathcal{R}$  while the qubit to be measured is in the set  $\mathcal{B}$ . This means that when an qubit-ancilla pair is in the wrong configuration we must first shuttle both qubits one step to the left (or both the the right). Note that this takes two additional shuttling operations, which means it is important to keep track at all times where on the BOARDSTATE the qubit and its ancilla are or else incur a shuttling overhead (which might become significant when dealing with large systems and many simultaneous measurements). We will deal with this problem of qubit-ancilla pair placement in more detail in section 3.3.

Secondly, assuming that the qubit-ancilla pair is in the right configuration to perform the PSB process one still needs to perform a shuttling-like operation to actually perform the measurement. On the technical level, the operation is different from coherent shuttling, but the use of the lines is similar with the difference that after the readout, the shuttling-like operation is undone by the use of the same lines as before—which are not necessarily the lines one would use to reverse a coherent shuttling operation. However, scheduling measurement events on the QDP is at least as hard as the scheduling of shuttle operations discussed above. Depending on the state the qubit is in, it will now assume one of two possible states that can be distinguished by their charge distribution.

Thirdly, the readout process requires to have a barrier line that borders to the qubit pair, with an empty dot is across the spot of the qubit to be measured. This is a consequence of the readout procedure.

In table 1 we introduce the measurement OPCODE M[i, j, k] with  $k \in \{1, 1\}$  to denote a measurement of a qubit at location (*i*, *j*) with an ancilla located to the left (k = 1) or to the right (k = 1).

#### 2.3.3. Single-qubit rotations

There are two ways in which single-qubit rotations can be performed on the QDP, both with drawbacks and advantages. The first method, which we call the semi-global qubit rotation, relies on electron-spin-resonance [15]. Its implementation in the QDP allows for any rotation in the single-qubit special unitary group SU(2) [16] to be performed but we do not have parallel control of individual qubits. The control architecture of the QDP is such that we can merely apply the same single-qubit unitary rotation on all qubits in either  $\mathcal{R}$  or  $\mathcal{B}$  (even or odd numbered columns). Concretely we can perform in parallel the single-qubit unitaries

$$U_{\mathcal{R}} = \bigotimes_{(i,j)\in\mathcal{R}} U_{i,j} \quad U \in SU(2)$$

(1)

$$U_{\mathcal{B}} = \bigotimes_{(i,j)\in\mathcal{B}} U_{i,j} \quad U \in SU(2),$$

<sup>(2)</sup>

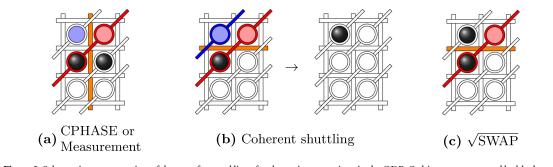

where  $U_{i,j}$  means applying the same unitary U to the state carried by the qubit at location (i, j). In general the only way to apply an arbitrary single-qubit unitary on a single qubit in  $\mathcal{B}$  (or  $\mathcal{R}$ ) is by applying the unitary to all qubits in  $\mathcal{B}$  ( $\mathcal{R}$ ), moving the desired qubit into an adjacent column, i.e. from  $\mathcal{B}$  to  $\mathcal{R}$  ( $\mathcal{R}$  to  $\mathcal{B}$ ) and then applying the inverse of the target unitary to  $\mathcal{R}$  ( $\mathcal{B}$ ). This restores all qubits except for the target qubit to their original states and leaves the target qubit with the required unitary applied. The target qubit can then be shuttled to its original location. A graphical depiction of the BOARDSTATE associated with this maneuver can be found in figure 3. This means applying a single unitary to a single qubit takes a constant amount of grid operations regardless of grid size.

The second method does allow for individual single-qubit rotations but is limited to performing single-qubit rotations of the form

$$U(\phi) = e^{i\phi Z}, \qquad Z = \begin{pmatrix} 1 & 0\\ 0 & -1 \end{pmatrix}, \quad \phi \in [0, 2\pi)$$

(3)

This operation can be performed on a given qubit  $|\psi\rangle_{(i,j)}$  by shuttling it from (i, j) to  $(i, j \pm 1)$ . When the qubit leaves the column it was originally defined ( $\mathcal{B}$  to  $\mathcal{R}$  or vice versa) it will effectively start precessing about its Z axis [4]. This effect is always present but it can be mitigated by timing subsequent operations such that a full rotation happens between every operation (effectively performing the identity transformation, see section 2.3.1). By changing the timing between subsequent operations any rotation of the form equation (3) can be effected. This technique will often be used to perform the Z-gate (defined above) and the  $S = \sqrt{Z}$  phase gate in error correction sequences.

#### 2.3.4. Two-qubit gates

As the last elementary tool, we have the ability to apply entangling two-qubit gates on adjacent qubits. The QDP can perform two different types of two-qubit gates. Inside one column, so between qubits at locations (i, j) and  $(i \pm 1, j)$ , a square-root of SWAP ( $\sqrt{\text{SWAP}}$ ) can be realized [17]. This can be done by lowering the horizontal barrier between the two qubits and toggling the voltage on the diagonal lines overhead the two qubits. This

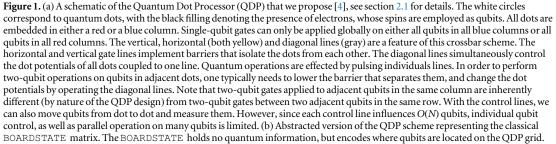

**Figure 2.** Schematic representation of the use of control lines for the native operations in the QDP. Qubits are represented by black balls on the grid. Red or blue colored dots are empty, but their dot potentials change due to an operation of the diagonal line they are coupled to. Empty dots unaffected by grid operations are white. (a) Vertical shuttling of a qubit (to the top dot) requires to lower the orange barrier. One can than either raise the dot potentials on the red diagonal line, or lower the potential on the blue dot by addressing the blue diagonal. (b) Schematic representation of the control lines used for performing two-qubit  $\sqrt{SWAP}$  gate between the two qubits on that grid. The orange barrier is lowered and the red diagonal line is utilized to detune dot potentials. (c) Grid operations necessary to perform a measurement or a two-qubit effective CPHASE gate between the two qubits is lowered, and the dot potentials along the red diagonal line is raised by pulsing the latter. Note that the empty, red colored dot is also effected by that action, and its barrier to the adjacent dot is lowered. If the two dots in the upper row were not empty, side effects would occur. See section 2.3.4 for more information on the nature of the two-qubit gates. Note also that the readout procedure of the measurement requires us to have the upper dot (light blue) empty, if the barrier gate between them is used for readout.

Figure 5. BOARDSTATE schematic for applying the unitary U to a single qubit (red). Time flows from left to right in the schematic. This process illustrates both, the possibility to retain single-qubit control by using coherent shuttling, and the overhead that comes with it. (a) We firstly apply the unitary U (blue bars) to all qubits in  $\mathcal{R}$  ( $\mathcal{B}$ ). We then move the qubit to the adjacent column. Note that this takes two operations because we do not want any other qubits transitioning with it. In (b), we apply the inverse unitary  $U^{\dagger}$  to all qubits in  $\mathcal{R}$  ( $\mathcal{B}$ ). In the last step we move the red qubit back, such that it is in its original position in (c).

situation is illustrated in figure 2(c). The  $\sqrt{SWAP}$  gate is defined as

$$\sqrt{\text{SWAP}} = \begin{pmatrix} 1 & (1+i)/2 & (1-i)/2 \\ (1-i)/2 & (1+i)/2 \\ & & 1 \end{pmatrix},$$

(4)

in the computational basis. Alternatively, between horizontally adjacent qubits, e.g. between  $(i, j) \in \mathcal{R}$  and  $(i, j \pm 1) \in \mathcal{B}$  the native two-qubit gate is an effective CPHASE gate which has matrix representation

$$CPHASE = \begin{pmatrix} 1 & & \\ & e^{i\phi_1} & \\ & & e^{i\phi_2} \\ & & & 1 \end{pmatrix},$$

(5)

in the computational basis and with the two angles  $\phi_1 + \phi_2 \mod 2\pi = \pi$  (demonstrated in [18–20]). This gate can be performed between horizontally adjacent qubits by lowering the vertical barrier between them and toggling the overhead diagonal lines. This is illustrated in figure 2(b). In practice we expect the  $\sqrt{SWAP}$  gate to have significantly higher fidelity than the CPHASE gate [4] so in any application (e.g. error correction) the  $\sqrt{SWAP}$  gate is the preferred native two-qubit gate on the QDP. In table 2 we define OPCODES for the horizontal interaction (CPHASE) and the vertical interaction ( $\sqrt{SWAP}$ ).

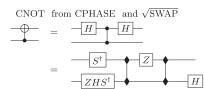

**Figure 4.** Construction of the CNOT gate out of the native CPHASE and  $\sqrt{SWAP}$  gates. Note that one requires two  $\sqrt{SWAP}$  gates to construct a CNOT gate [21]. When performing arbitrary algorithms it would be preferable to forgo this substitution and instead compile the algorithm directly into a gateset containing the  $\sqrt{SWAP}$  gate.

**Table 2.** OPCODES for horizontal and vertical two-qubit operations on the QDP, respectively the CPHASE and  $\sqrt{SWAP}$  gates. We alsoinclude OPCODES for the performing of CNOT gates composed of  $\sqrt{SWAP}$  or CPHASE gates.

| OPCODE    | Effect                                                              | Parameter                          |

|-----------|---------------------------------------------------------------------|------------------------------------|

| HI[(i,j)] | Perform CPHASE gate between sites $(i, j)$ and $(i, j+1)$           | $(i, j) \in [0: N - 2]^{\times 2}$ |

| VI[(i,j)] | Perform $\sqrt{SWAP}$ gate between sites $(i, j)$ and $(i+1, j)$    | (i, j) $\in [0: N - 2]^{\times 2}$ |

| HC[(i,j)] | Perform CNOT (using CPHASE) between $(i, j)$ and $(i, j+1)$         | (i, j) $\in [0: N - 2]^{\times 2}$ |

| VC[(i,j)] | Perform CNOT (using $\sqrt{SWAP}$ ) between $(i, j)$ and $(i+1, j)$ | (i, j) $\in [0: N - 2]^{\times 2}$ |

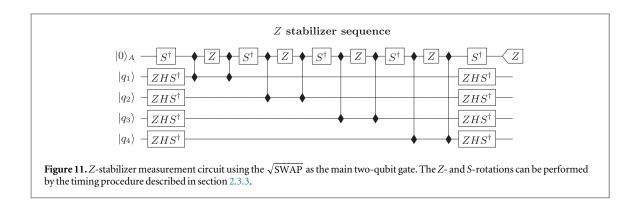

#### 2.3.5. CNOT subroutine

Many quantum algorithms are conceived using the CNOT gate as the main two-qubit gate. However the QDP does not support the CNOT gate natively. It is easy to construct the CNOT gate from the CPHASE gate by dressing the CPHASE gate with single-qubit Hadamard rotations as seen in figure 4 (left). It is slightly more complicated to construct a CNOT gate using the  $\sqrt{SWAP}$  but it can be done by performing two  $\sqrt{SWAP}$  gates interspersed single-qubit rotations [19–21] as seen in figure 4 (right). If the control qubit is moved from an adjacent column on the QDP (as it is in most cases we will deal with) the *Z* and *S*-gates can be performed by the *Z*-rotation-by-waiting technique described in the last section. For completeness we also define an OPCODE for the CNOT operation in table 2.

# 3. Parallel operation of a crossbar architecture

In this section we focus on performing operations in parallel on the QDP (or more general crossbar architectures). Because of the limitations imposed by the shared control lines of the crossbar architecture, achieving as much parallelism as possible is a non-trivial task. We will discuss parallel shuttle operations, parallel two-qubit gates, parallel single-qubit gates and parallel measurement. As part of the focus on parallel shuttling we also include some special cases relevant to quantum error correction where full parallelism is possible.

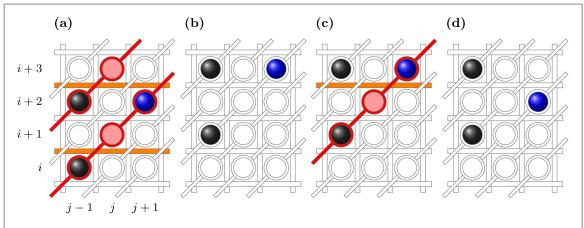

Before we start our investigation however, we would like to put three issues into focus that are likely to be encountered when attempting parallel operations. Firstly, it must be understood that an operation on one location on a crossbar system can cause unwanted side effects in other locations (that might be far away). As indicated in section 2 many elementary operations on the grid in particular take place at the crossing points of control lines. This means that any parallel use of these grid operations must take into account 'spurious crossings' which may have such unintended side effects. We can illustrate this with an example. Imagine we want to perform the vertical shuttling operations VS[i, j-1, 1] and VS[i+2, j-1, 1] in parallel (see figure 5 for illustration). We can do this by lowering the horizontal barriers at rows *i* and *i* + 2 (orange in illustration) and elevating the on-site potentials on the diagonal lines i - j + 1 and i + 2 - j + 1 (red in illustration). This will open upwards flows at locations (i, j - 1) and (i + 2, j - 1). However it will also open an upward flow at the location (i + 2, j + 1). This means, if a qubit is present at that location an unintended shuttling event will happen. To avoid this outcome we must either perform the operations VS[i, j-1, 1] and VS[i+2, j-1, 1] in sequence (taking two time-steps) or perform an operation VS[i+2, j+1, -1] to fix the mistake we made, again taking two time-steps. This is a general problem when considering parallel operations on the QDP.

Secondly, we would like to point out that in realistic setups, we expect a trade-off between parallelism (manifested in algorithmic depth) and operation fidelity (in particular this will be the case in the QDP system). In order to understand this, we have to be aware that most operations consist of applying the correct pulses for the right amount of time. These durations however can slightly vary from site to site (due to manufacturing imperfections), so we e.g. must be able to switch barriers back on again prematurely when accounting for a site with a shorter time required. If this is not possible (maybe because it would cause side effects) a loss in operation fidelity is a consequence of the resulting improperly timed operation. The most robust case is thus to schedule

**Figure 5.** Spurious shuttle operations. Here we illustrate an example of unintended side effects that occur due to the limited control. We again denote qubits by colored balls, and color barriers and lines that are operated. Empty dots with changed potentials are colored as well, white dots are unaffected. (a) The black qubits are to be shuttled from (i, j - 1) to (i + 1, j - 1) and from (i + 2, j) to (i + 3, j) respectively without moving the blue qubit. For that purpose, the (orange) barriers between the two-dot pairs are lowered, as well as the (red) diagonal lines through (i, j - 1) and (i + 2, j) are pulsed, such that the dot potentials on those sites are raised. (b) The qubit on (i + 3, j + 1) has unintentionally moved to (i + 2, j + 1). (c) To remedy this situation, we lower the barrier number i + 2 again (orange), and also raise the potential on (i + 3, j + 1) and all other dots that are connected by the pulsed diagonal line (red). In (d), the desired situation is achieved.

operations line-by-line. By this we mean that we attempt to perform O(N) grid operations in a time step while using every horizontal, diagonal or vertical line only once per individual grid operation. If we for instance schedule several vertical shuttle operations, we may choose to start by lowering one of horizontal barrier first and then detune the dot potentials of all qubits adjacent to that barrier, by pulsing the corresponding diagonal lines. To account for the variations, we reset the diagonal lines at slightly different times. Line-by-line operations work with either line types for every two-dot operation (measurement, shuttling and two-qubit gates). Note however that for shuttling operations individual control over one line is sufficient, whereas for measurement and twoqubit gates we would ideally like to be able to control two lines per qubit pair individually, where one line should be the barrier separating the two paired qubits. Results presented in the following take into account these constraints for quantum error correction. The parallel operation nonetheless remains one of the greatest challenges of the crossbar scheme. In this section we will assume all operations to be perfect (even when performed in parallel) but in section 5 we perform a more detailed analysis of the behavior of the QDP when operational errors are taken into account.

Thirdly, from a performance perspective it is important to separate the operations that have to be done on the qubits on the crossbar grid from operations that can be done by classical side computation (which for our purposes is essentially free). We will deal with this by including classical side computation in the OPCODES for parallel operation. This way the complexity of dealing with spurious operations is abstracted away. We devise algorithms that take in an arbitrary list of shuttling or two-qubit gate locations and work out a sequence of shuttling or two-qubit gate steps that achieve that list. We begin with discussing parallel shuttle operations.

| ······································ | 1 ··· ·· - E · ) · 1 ···                                                                   |

|----------------------------------------|--------------------------------------------------------------------------------------------|

| OPCODE                                 | Effect                                                                                     |

| HS[L]<br>VS[L]                         | Perform HS[i,j,k] for all $(i, j, k) \in L$<br>Perform HS[i,j,k] for all $(i, j, k) \in L$ |

**3.1. Parallel shuttle operations** We define parallel versions of the shuttling OPCODES HS[i, j, k] and VS[i, j, k] as

This code takes in a set (denoted as L) of tuples (i, j, k) which denote 'locations at which shuttling happens' (i, j) and 'shuttling direction' (k). From these codes it is not immediately clear how many of the shuttling operations can be performed in a single grid operation, i.e. setting the diagonal lines to some configuration and lowering several horizontal or vertical barrier. If multiple grid operations are needed (such as in the example figure 5) we would like this sequence of grid operations to be as short as possible. However, given some initial BOARDSTATE and a parallel shuttling command HS [L] it is not clear what the sequence of parallel shuttling operations actualizing this command is. Below we analyze this problem of parallel shuttling in more detail and give a classical algorithm that produces, from an input HS [L] or VS [L] a sequence of parallel grid operations that performs this command. Ideally we would like this sequence to be as short as possible. This algorithm does

not perform optimally in all circumstances (i.e. it does not produce the shortest possible sequence of parallel shuttling operations) but for many relevant cases it performs quite well. Note that this is a technical section and the details are not needed to understand the quantum error correction results in section 4, 4.4 and 4.5. Readers interested only in those may skip ahead to section 3.2.

#### 3.1.1. The flow matrix

We will only consider shuttling to the left and to the right but all mechanisms introduced work equally well for shuttling in the vertical directions. As will be seen in section 3.4 some BOARDSTATE configurations can be converted into each other in an amount of grid operations that is constant in the size of the grid. It can be seen that the problem of whether two shuttles can be performed in parallel is a problem with a matrix structure, as flows can only occur at the intersection open barriers and non-trivial diagonal line gradients. To capture this matrix intuition we construct, from the initial BOARDSTATE and the command HS [L] a matrix *F* which we call the flow matrix. This matrix will have entries corresponding to the crossing of the gradient line between two diagonal qubit lines and the vertical barrier lines. The flow matrix is defined with respect to a specific command HS [L] and its entries correspond to the locations on the grid where we want shuttling in certain directions to happen.

From a specific command HS[L] and a specific current BOARDSTATE we will define a flow matrix *F*. This matrix will have entries which take value in the set {*r*, *l*, *e*, *re*, *le*, \*}. Each element of this set has a specific operational meaning. The elements *r*, *l*, *e* correspond to specific actions that can be taken on the qubit grid. They correspond specifically to 'shuttle to the right' (*r*), 'shuttle to the left' (*l*) and 'do nothing' (*e*). Note that these actions do not necessarily act on a fixed qubit. Rather they act on a specific location on the grid (where a qubit may or may not be present). The other three elements do not directly correspond to a shuttling action but rather signify that at this location we have a choice of different consistent actions. We will call these elements 'wildcards'. These wildcards signify the actions 'shuttle to the right or do nothing' (*re*), 'shuttle to the left or do nothing' (*le*), or 'any action is allowed' (\*).

We fill in the matrix entry  $F_{ij}$  with a symbol r for every (i, j, 1) in L. This indicates that at some point in time we want to perform the operation HS [i, j, 1] at that location. Similarly we fill in a symbol l on every matrix entry  $F_{ij}$  for every (i, j + 1, -1) in L. We place the symbols re, le respectively on the matrix entries  $F_{i(j-1)}$  and  $F_{ij}$  for every occupied site (i, j) in the BOARDSTATE that has no corresponding entry in L. This indicates that we would like for no shuttle operations to happen on these crossing points (since we want the qubit to stay put) but that we do not mind a HS [i, j-1, 1] happening on the crossing point to the left of the qubit at (i, j) (since it will not affect the qubit) or mind a HS [i, j, 1] happening to the right of the qubit at (i, j). Lastly we fill in the symbol e on every matrix entry  $F_{ij}$  where we want no shuttling operation to happen at any time to the right of the site (i, j) (for instance on the crossing point between two qubits that are in horizontally adjacent sites). In every other matrix entry  $F_{ij}$  we fill in the wildcard symbol \* indicating that we do not care if any operation happens at this crossing point. Let's summarize the above construction by

|                            | ſr | if | $(i, j, 1) \in L$                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------|----|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | 1  | if | $(i, j, 1) \in L$<br>$(i, j, 1) \in L$                                                                                                                                                                                                                                                                                                                                                                                                         |

| Е                          | e  | if | (BOARDSTATE $(i, j) = 1 \land$ BOARDSTATE $(i, j + 1) = 1) \land ((i, j, k) \not\in L, k \in \{1, -1\})$<br>(BOARDSTATE $(i, j) = 0 \land$ BOARDSTATE $(i, j + 1) = 1) \land ((i, j, k) \not\in L, k \in \{1, -1\})$<br>(BOARDSTATE $(i, j) = 1 \land$ BOARDSTATE $(i, j + 1) = 0) \land ((i, j, k) \not\in L, k \in \{1, -1\})$<br>(BOARDSTATE $(i, j) = 0 \land$ BOARDSTATE $(i, j + 1) = 0) \land ((i, j, k) \not\in L, k \in \{1, -1\})$ . |

| $\Gamma_{ij} = \mathbf{K}$ | re | if | (BOARDSTATE $(i, j) = 0 \land$ BOARDSTATE $(i, j + 1) = 1) \land ((i, j, k) \not\in L, k \in \{1, -1\})$                                                                                                                                                                                                                                                                                                                                       |

|                            | le | if | (BOARDSTATE $(i, j) = 1 \land$ BOARDSTATE $(i, j + 1) = 0) \land ((i, j, k) \notin L, k \in \{1, -1\})$                                                                                                                                                                                                                                                                                                                                        |

|                            | *  | if | (BOARDSTATE $(i, j) = 0 \land$ BOARDSTATE $(i, j + 1) = 0) \land ((i, j, k) \not\in L, k \in \{1, -1\}).$                                                                                                                                                                                                                                                                                                                                      |

The flow matrix *F* takes values in the set {*r*, *l*, *e*, *re*, *le*, \*}. In supplementary material is available online at stacks.iop.org/QST/3/035005/mmedia we discuss the mathematical structure of this set in more detail. The above construction gives us a matrix of operations we would like to apply to the initial BOARDSTATE. You can see an example of a BOARDSTATE and HS [L] command with corresponding flow matrix *F* in figure 6.

#### 3.1.2. An algorithm for parallel shuttling

The task is now to subdivide the flow matrix *F* into a sequence of shuttling operations that can be performed in parallel. Ideally we would like this sequence to be as short as possible. One simple way to generate a sequence of this form, as described in the beginning of the section, is to perform all operations one column at a time, i.e. lowering the first vertical barrier, setting the required gradients to shuttle every qubit adjacent to that vertical barrier and then move on to the second vertical barrier and so on. This yields a sequence of parallel shuttling operations of depth *N*. This solution is always possible for any flow matrix *F*. However, as can be seen in section 3.4 for some flow matrices this is far from an optimal solution. Below we set out in detail an algorithm

**Table 3.** Table listing the time complexity and relative power of the **CheckIndependence(**) and **IndependenceSet(**) for three different classes of subroutine. The parameters *N* and *M* are the size of the QDP grid and the size of the input set *S* respectively. The subroutine classes 'simple' and 'greedy commutative' can be run in polynomial time while the class 'k-commutative' is fixed-parameter-tractable, with independent parameter *k*. This subroutine yields increasingly better results (shorter shuttling sequences) for increasing *k* but the time complexity grows rapidly with *k*. See supplementary material for a detailed description of these subroutines. For an illustration of the advantages of these algorithms, one can consider the shuttle commands given in section 3.4. A naive line-by-line approach will take *N* time-steps while it is easy to see that the above algorithms find sequences of length one.

| Name               | Time Complexity                                                                                              | Relative power                                                                  |

|--------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Simple             | O(CheckIndependence $()) = O(NM)O($ IndependenceSet $()) = O(NM)$                                            | Shorter sequences than line-by-line.                                            |

| k-commutative      | $O($ <b>CheckIndependence</b> $()) = O(NMM^{k}k^{4})$<br>$O($ <b>IndependenceSet</b> $()) = O(NMM^{k}k^{4})$ | Shorter sequences than 'Simple'.<br>Shorter sequences for increasing <i>k</i> . |

| Greedy commutative | $O($ CheckIndependence $()) = O(NM^3)$<br>$O($ IndependenceSet $()) = O(NM^3)$                               | Shorter sequences than 'Simple'.<br>Relation to 'k-commutative' unknown.        |

that finds better (shorter sequences) solutions for many flow matrices. The algorithm is based on the idea that some columns of the flow matrix *F* can be 'dependent' on each other. For instance two columns could be composed of the exact same operations (up to a shift accounting for the fact that the diagonal lines do not run along the rows but diagonally). This means we can perform the shuttle operations in the two columns simultaneously by lowering barriers corresponding to these columns and setting the required gradient. More complicated forms of dependence are also possible. We can use dependence of columns to perform operations in parallel. For instance if a command HS [L] calls for exactly the same shuttling events to happen on two columns (up to a constant vertical shift proportional to the horizontal distance of the two columns) we can perform these shuttling operations in a single time step.

This notion of (in)dependence of columns is captured by a call to an 'independence subroutine'. We call these subroutines **CheckIndependence**(S, v) which takes in a set of columns S of the flow matrix F of and a column v of the flow matrix F and decides whether v is independent of the elements of S and **DependenceSet** (S, v) which takes in a set of columns S and a column v and returns a subset A of S containing all the columns on which v depends. We will discuss various versions of these subroutines leading to more or less refined notions of independence (and thus longer of shorter shuttling sequences) in supplementary material. We list all subroutines discussed in supplementary material in table 3 together with their relative power and time complexity. Here we just treat the subroutines as a given and build the algorithm around it. This algorithm does not always yield optimal sequences of parallel shuttling operations, but it can be run using a polynomial amount of classical side-resources given that the subroutine can be constructed efficiently, (see theorem 1) while we expect an algorithm that always produces optimal shuttling sequences to require exponential computational resources. Below we give a pseudo-code version of the algorithm. Note that this algorithm only produces sequences of parallel shuttling operations where the ordering of the operations does not matter. See supplementary material for more details on how this property is guaranteed.

(6)

#### Algorithm 1. Generate list of parallel shuttle operations

Input: Flow matrix F Output: List of shuttle operations L 1: 2: // We will consistently write columns of the flow matrix F as  $v_i$  where i indicates 3: // the column index of  $v_i$  in *F*. 4: 5: Set S to an empty list 6: 7: // Below we construct a set of independent columns S and sets of dependence  $A_i$  for the dependent columns  $v_i$ . 8: 9: for  $i \in [0: N - 2]$  do 10: **Set**  $v_i$  to the *i*'th column of *F* 11: //Check if the column  $v_i$  is independent of the columns already in the set S. This requires a 12: 13: // subroutine call to CheckIndependence. See appendix for the construction of this subroutine. 14: 15: if CheckIndependence(v<sub>i</sub>, S) is TRUE then 16: // The function  $\theta$  maps the symbols \*, re, le to e. We must do this since we want to make an operation 17: 18: // out of  $v_i$  later and the wildcard elements \*, re, le do not strictly correspond to operations. Other 19: // choices are possible here but in keeping with the idea of doing a 20: // minimal amount of operations, the mapping to e is a good choice. 21: Add  $\theta(v_i)$  to S 22: 23: **Set**  $A_i$  to  $\{v_i\}$ else 24: 25: Set  $A_i$  to DependenceSet $(S, v_i)$ 26: end if 27: end for 28: 29: // Initialize an empty ordered set that will contain all HS [L] commands in sequence. 30: 31: Set L to an empty ordered set 32: for  $v_i \in S$  do 33: // Initialize an empty set that will contain all tuples for a single  ${\tt HS}\,[\,{\tt L}\,]\,$  command. 34: 35: Set  ${\mathbb L}$  to an empty set 36: 37: for  $j \in [0: N - 2]$  do 38: 39: // Check if  $v_i$  is in the dependence set  $A_i$ . 40: 41: if  $v_i \in A_j$  then 42: // Loop over all components of  $v_i$ . 43: for  $k \in [0: length(v_i) - 1]$  do 44:  $//\phi$  maps the *r*, *l*, *e* valued column *v* to an 1, -1, 0 valued vector as  $\phi(r) = 1$ ,  $\phi(l) = -1$ ,  $\phi(e) = 0$ . 45: 46: if  $\phi[(v_i)_k] \neq 0$  then 47: 48: **Add**  $(j, k - (i - j), \phi[(v_i)_k])$  to L 49: end if end for 50: 51: end if 52: end for 53: Add HS[L] to L 54: end for 55: return L

**Theorem 1.** The algorithm described in algorithm 1 has a time complexity upper bounded by  $O(N^4) + N \cdot O(\text{CheckIndependence}(S, v_i)) + N \cdot O(\text{DependenceSet}(S, v_i)),$ where N is the number of columns in the input flow matrix F. The subroutines **CheckIndependence**(S,  $v_i$ ) and **DependenceSet**(S,  $v_i$ ) both take in a set S of independent columns of the flow matrix F and a column  $v_i$  of the flow matrix F and respectively check whether v is independent of the set S or produce a subset A of S on which v depends. Various versions of these subroutines are discussed in supplementary material and their time complexities are given in table 3.

**Proof.** Begin by noting that the algorithm 1 consists of two independent **For**-loops. The first **For**-loop (lines 2-11) calls its body N times (ignoring constant factors). Calling the **For**-loop body (lines 3-10) in the worst case requires calling both **CheckIndependence**() and **DependenceSet**() plus some constant time instructions. This means the first **For**-loop has a worst case complexity of

$N \cdot O(\text{CheckIndependence}()) + N \cdot O(\text{DependenceSet}()).$

The second **For**-loop (lines 13-25) consists of three nested **For**-loops of length O(N) with an **If**-clause inside the first two **For**-loops (line 16) constant time operation at the bottom (line 19). The first **For**-loop can be seen to be of order O(N) by noting that the set of independent columns *S* can be no bigger than *N* in which case all columns are independent. The second **For**-loop (line 15) is O(N) bounded by construction. Note that the **If**-clause on line 16 can take time O(N) to complete since for any dependency set  $A_j$  we can only say that  $|A_j| \leq N$  (since  $A_j$  is a subset of the set of all columns of *F*). The third loop is also O(N) bounded since length( $v_i$ )  $\leq N$  for all columns  $v_i$  of *F*. Tallying up all contributions we arrive at equation (6), which completes the argument.

This concludes our discussion of parallel shuttling operations. Before we move on however, it is worth pointing out an interesting example where this shuttling can be used a subroutine to perform more complicated operations. This example will also be of use later when discussing parallel measurement in section 3.3 and the mapping of quantum error correction codes in sections 4, 4.4, 4.5.

#### 3.1.3. Selective parallel single-qubit rotations

In this section we will discuss a particular example that illustrates the use of abstracting away the complexity of parallel shuttling. Imagine a QDP grid initialized in the so-called *idle* configuration. This configuration can be seen in figure 7. We will focus on the qubit in the odd columns (i.e. the set  $\mathcal{B}$ ). Imagine a subset *S* of these qubits to be in the state  $|1\rangle$  and the remainder of these qubits to be in the state  $|0\rangle$ . The qubits on in the set  $\mathcal{R}$  can be in some arbitrary (and possibly entangled) multiqubit state  $|\Psi\rangle$ . We would like to change the states states of the qubits in the set *S* to  $|0\rangle$  without changing the state of any other qubit. Due to the limited single-qubit gates (see section 2.3.3) available in the QDP this is a non-trivial problem for some arbitrary set *S*. However using the power of parallel shuttling we can perform this task as follows. Begin by defining the set  $\hat{S}$  to be the complement of *S* in  $\mathcal{R}$ . Now we begin by performing the parallel shuttling operation

$$HS[L], \quad L = \{(i, j, 1) \parallel (i, j) \in \hat{S}\}.$$

(7)

Here we abuse notation a bit by referring to  $\hat{S}$  as the set of locations of the qubits in  $\hat{S}$ . This operation in effect moves all qubits in  $\hat{S}$  out of  $\mathcal{R}$  (and into  $\mathcal{B}$ , note that the dots the qubits are being shuttled in are always empty because of the definition of  $\mathcal{R}$  (and into  $\mathcal{B}$ , note that the dots the qubits are being shuttled in are always empty because of the definition of  $\mathcal{R}$  (and into  $\mathcal{B}$ , note that the dots the qubits are being shuttled in are always empty because of the definition of  $\mathcal{R}$  (and into  $\mathcal{B}$ , note that the dots the qubits are being shuttled in are always empty because of the definition of  $\mathcal{R}$  (and into  $\mathcal{B}$ , note that the dots the qubits are being shuttled in are always empty because of the definition of  $\mathcal{R}$  (and into  $\mathcal{B}$ , note that the dots the qubits in section 2.3.3) to perform an *X*-rotation on all qubits in  $\mathcal{R}$ , which is now just all qubits in the set *S*. This flips changes the states of the qubits in *S* from  $|1\rangle$  to  $|0\rangle$  without changing the state of any other qubit. Following this we can restore the BOARDSTATE to its original configuration by applying the parallel shuttling command

$$HS[L], \quad L = \{(i, j, -1) \parallel (i, j) \in \hat{S}\}.$$

(8)

Now we have applied the required operation. Note that at no point we had to reason about the structure of the set *S* itself. This complexity was taken care of by the classical subroutines embedded in HS[L]. Next we discuss performing parallel two-qubit gates.

#### 3.2. Parallel two-qubit gates

Similar to parallel shuttling it is in general rather involved to perform parallel two-qubit operations in the QDP. We can again define parallel versions of the OPCODES for two-qubit operations and then analyze how to perform them as parallel as possible (again having access to classical side computation).

| OPCODE | Effect                                        |

|--------|-----------------------------------------------|

| HI[L]  | Perform VI[( $i, j$ )] for $(i, j) \in L$     |

| VI[L]  | Perform HI[( $i, j$ )] for ( $i, j$ ) $\in$ L |

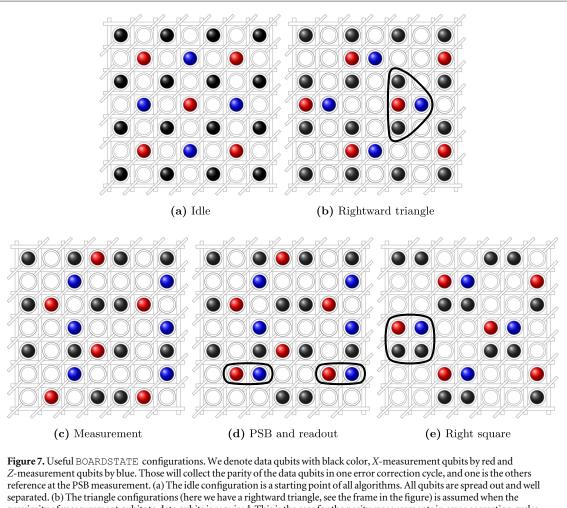

Preference at the PSB measurement. (a) The idle configuration is a starting point of all algorithms. All qubits are spread out and well separated. (b) The triangle configurations (here we have a rightward triangle, see the frame in the figure) is assumed when the proximity of measurement qubits to data qubits is required. This is the case for the parity measurements in error correction cycles. (c) The measurement configuration is formed to bring X- and Z-measurement qubits close to each other, such that a row can be selected in which the measurement is performed. (d) Certain measurement qubits are brought to adjacent dots in order to perform the PSB-based measurement and readout in a line-by-line fashion (encircled qubits). Since the rest of the grid is in the measurement configuration is a mid-way point between the idle and (right) triangle configuration. Going through the square configuration keeps the shuttling algorithm manageable, as not more that 2 different heights of the dot potentials are employed. One of the characteristic squares is framed in the figure.

Given an BOARDSTATE and a HI [L] command one could use an algorithm similar to the algorithm presented for shuttling. We can again construct a matrix F such that  $F_{ii} = 1$  is for all tuples (i, j) in L indicating the locations where we desire a two-qubit operation to happen and  $F_{ij} = 0$  everywhere else. Now we can use the algorithm presented above for shuttling to decompose the matrix *F* into a series of parallel HI [L] operations. However, since we have  $CPHASE^2 = I$  the independence subroutine reduces to linear independence of the columns of F modulo 2. This means we can find an optimal decomposition into parallel operations by finding the Schmidt-normal [22, Chapter 14] form of the matrix F (Note that we do have to 'tilt' the matrix F to account for the fact that as posed the diagonal lines of the matrix F are its 'rows'). We can make the same argument given a BOARDSTATE and a VI [L] command but now the Schmidt-normal form must be found modulo 4 as  $(\sqrt{\text{SWAP}})^4 = \mathbb{I}$ . As both addition modulo 2 ( $\mathbb{Z}_2$ ) and addition modulo 4 ( $\mathbb{Z}_4$ ) are principal ideal domains both of the Schmidt-normal forms can be found efficiently and generate optimal sequences of parallel two-qubit interactions. The depth of the sequence of operations is now proportional to the rank of the matrix F over  $\mathbb{Z}_2$ (CPHASE) or  $\mathbb{Z}_4$  ( $\sqrt{\text{SWAP}}$ ). However, as mentioned before, the parallel operation of two-qubit gates in the QDP will mean taking a hit in operation fidelity vis-a-vis the more controllable line-by-line operation [4]. Since this operation fidelity is typically a much larger error source than the waiting-time-induced decoherence stemming from line-by line operation we will for the remainder of the paper assume line-by-line operation of the two-qubit gates. This will have an impact when performing quantum error correction on the QDP which we will discuss in more detail in section 5.

For the sake of completeness we also define a parallel version of the CNOT OPCODE. The same considerations of parallel operation hold for the parallel use of CNOT gates as they hold for the CPHASE and  $\sqrt{\text{SWAP}}$  gates. We continue the discussion of parallelism in the QDP by analyzing parallel measurements.

| OPCODE | Effect                                        |

|--------|-----------------------------------------------|

| VC[L]  | Perform VC [ (i, j) ] for every $(i, j)$ in L |

#### 3.3. Parallel measurements

Performing measurements on an arbitrary subset of qubits on the QDP is in general quite involved. Every qubit to be measured requires an ancilla qubit and this ancilla qubit must be in a known computational basis state, and an empty dot must be adjacent as a reference for the readout process. The qubits must then be shuttled such that they are horizontally adjacent to their respective ancilla qubits and must also be located in such a way such that they are in the right columns for the PSB process to take place (revisit section 2.3.2 for more information). This can be done using the algorithm for parallel shuttling presented above but in the worst case this will take a sequence of depth O(N) parallel shuttle operations. On top of the required shuttling the PSB process itself (from a control perspective similar to shuttling) must be performed in a way that depends on the BOARDSTATE and the configuration of the qubit/ancilla pairs. In general this PSB process will be performed line-by-line (for the fidelity reasons mentioned in the beginning of the section) and hence requires a sequence of depth O(N) parallel grid operations (plus the amount of shuttling operations needed to attain the right measurement configuration in the first place). Due to this complexity we will not analyze parallel measurement in detail but rather focus on a particular case relevant to the mapping of the surface code. But first we define a parallel measurement OPCODE M[L] which takes in a list of tuples (i, j, k) denoting locations of qubits to be measured (i, j) and whether the ancilla qubit is to the left (k = -1) or to the right (k = 1) of the qubit to be measured.

| OPCODE | Effect                                              |

|--------|-----------------------------------------------------|

| M[L]   | Perform M[ $(i, j, k)$ ] for every $(i, j, k)$ in L |

#### 3.3.1. A specific parallel measurement example

Let us consider a specific example of a parallel measurement procedure that will be used in our discussion of error correction. We begin by imagining the BOARDSTATE to be in the *idle* configuration (figure 7 top left). We next perform the shuttle operations needed to change the BOARDSTATE to the *measurement* configuration. This configuration (and how to reach it by shuttling operations from the idle configuration) will be discussed section 3.4 and can be seen in figure 7(c). Next take the qubits to be measured in the parallel measurement operation to be the red qubits in figure 7. The qubits directly to the right or to the left of those qubits will be the required readout ancillas (blue in figure 7). We will assume that the readout ancillas are in the  $|0\rangle$  state. If some ancilla qubits are in the  $|1\rangle$  state instead we can always perform the grid. Note that all the ancilla qubits are in the set  $\mathcal{B}$  whereas the qubits to be read out are in the set  $\mathcal{R}$ . This means that we can perform the PSB process by attempting to shuttle the qubit to be measured (red) into the sites occupied by the ancilla qubits (blue). In principle we could perform this operations in parallel by executing the operations

$$IS[L], \quad L = \{(i, j, 1) \mid | i = 0 \mod 2, j = 1 \mod 2, i + j = 1 \mod 4\}$$

(9)

to bring the qubits to be measured (red) horizontally adjacent to the ancilla qubits (blue) and then

$$M[L], L = \{(i, j, 1) \mid i = 1 \mod 4, j = 1 \mod 4\}$$

(10)

and

$$\mathbb{M}[L], \ L = \{(i, j, -1) \mid | i = 3 \mod 4, j = 3 \mod 4\}.$$

(11)

All of these operations can be performed in a single time step. However for fidelity and control reasons laid out in the beginning we would prefer to perform these operations in a line-by-line manner. In particular we would like to perform these operations one row at a time since this gives us the ability to control both diagonal and vertical lines individually for each measurement. However we must take care to avoid spurious operations. For instance when performing measurements on the qubits at locations (1, 1) and (1, 5) we must avoid also performing a measurement on the qubit at location (5, 5). To avoid this situation we will bring only the bottom row of qubits to be measured horizontally adjacent to the ancilla qubits, perform the PSB process and readout on that row only and then shuttle the qubits to be measured back down again. This we repeat going up in rows until we reach the end of the grid. More formally we perform the following sequence of operations.

Algorithm 2. Loop over OPCODES to perform line-by-line measurements

1: for  $i \in [0: N - 2]$  do 2: if  $i = 1 \mod 4$  then 3: VS[L],  $L = \{(i - 1, j, -1) || j = 1 \mod 4\}$ 4:  $M[L], L = \{(i, j, 1) || j = 1 \mod 4\}$ 5: VS[L],  $L = \{(i - 1, j, 1) || j = 1 \mod 4\}$ end if 6: if  $i = 3 \mod 4$  then 7: VS[L],  $L = \{(i - 1, j, -1) || j = 3 \mod 4\}$ 8: 9:  $M[L], L = \{(i, j, -1) || j = 3 \mod 4\}$ 10: VS[L],  $L = \{(i - 1, j, 1) || j = 3 \mod 4\}$ 11: end if 12: end for

We will use this particular procedure when performing the readout step in a surface code error correction cycle in section 4.4. This concludes our discussion of parallel operation on the QDP. We now move on to highlight some BOARDSTATE configurations that will feature prominently in the surface and color code mappings.

### 3.4. Some useful grid configurations

There are several configurations of the BOARDSTATE that show up frequently enough (for instance in the error correction codes in section 4.4) to merit some special attention. In this section we list these specific configurations and show how to construct them.

#### 3.4.1. Idle configuration

The idle configuration is the configuration in which the QDP is initialized. As shown in figure 7 it has a checkerboard pattern of filled and unfilled sites. In this configuration no two-qubit gates can be applied between any qubit pair but since it minimizes unwanted crosstalk between qubits [4], it is good practice to bring the system back to this configuration when not performing any operations. For this reason we consider the idle configuration to be the starting point for the construction of all other configurations.

#### 3.4.2. Square configuration

As seen in figure 7(e) the square configurations consist of alternating filled and unfilled  $2 \times 2$  blocks of sites. The so-called right square configuration can be reached from the idle configuration by a shuttling operation HS [L] with the set L being

$$L = \{(i, j, 1) \mid i = 1 \mod 2, \\ j = 1 \mod 2, i + j = 2 \mod 4\} \cup \{(i, j, -1) \mid i = 0 \mod 2, \\ j = 1 \mod 2, i + j = 3 \mod 4\}.$$

(12)

Note that this operation only takes a single time step, the square configuration is shown in figure 7(e). The right square configuration is characterized by the red (*Z*-) ancilla being in the left corner of every square. Another flavor of this configuration is the left square configuration, where the red ancilla is in the upper right corner, and the blue one in the left. The left square configuration can be reached from the idle configuration by a shuttling operation HS [L] with the set L being.

$$L = \{(i, j, 1) \mid | i = 0 \mod 2, \\ j = 0 \mod 2, i + j = 2 \mod 4\} \cup \{(i, j, -1) \mid | i = 1 \mod 2, \\ j = 0 \mod 2, i + j = 1 \mod 4\}.$$

(13)

These configurations are used as an intermediate step for us to reach the triangle configurations.

#### 3.4.3. Measurement Configuration

The measurement configuration can be reached from the idle configuration in three time-steps by the following sequence of parallel shuttling operations.

HS[A],

$$A = \{(i, j, -1), (i - 1, j - 1, 1) || i = 1 \mod 4, j = 2 \mod 4\},$$

HS[B],  $B = \{(i - 1, j - 1, 1) || i = 3 \mod 4, j = 1 \mod 4\},$

VS[C],  $C = \{(i, j, -1) || i = 0 \mod 2, j = 1 \mod 2, i + j = 1 \mod 4\}.$  (14)

This configuration can be seen in figure 7(d) and it is an intermediate state in the measurement process of the blue qubits using the red qubits as ancillas. How this measurement protocol works in detail is described in section 3.3.

#### 3.4.4. Triangle configurations

In order to collect the parity of the data qubits in the error correction cycles, we need to align the ancilla qubits with the data qubits, according to the two-qubit gates used. This is reflected in the use of triangle configurations. There are two triangle configurations that can be reached in a single parallel shuttling step from the right square configuration. The first one, seen in figure 7(b), is called the rightward triangle configuration. It can be reached from the square configuration by the grid operation HS [L] with the set L being

$$L = \{(i, j, -1) \mid 0 = 1 \mod 2, j = 1 \mod 2, i + j = 3 \mod 4\},$$

(15)

which does as much as to shuttle the right data qubit of every square (framed squares in figure 7(e)) to the empty dot on its right. In this configuration, we are able to perform high-fidelity two-qubit gates between the two data qubits and the ancilla in every triangle. In order to reach the neighboring pair of data qubits with the same ancilla, we start from the left square configuration and shuttle the left data qubit to the left. Operationally, we would do HS[L] with

$$L = \{(i, j, 1) \mid | i = 0 \mod 2, j = 0 \mod 2, i + j = 2 \mod 4\}.$$

(16)

Note again that these parallel shuttling operations can be performed in a single time step. From these configurations the idle configuration can also be reached in a single time step. In the next section these configurations will feature prominently in the mapping of several quantum error correction codes to the QDP architecture.

# 4. Error correction codes

In this section we will apply the techniques we developed in the previous sections to map several quantum error correction codes to the QDP.

#### 4.1. Introduction

First we recall some basic facts about quantum error correction codes and topological stabilizer codes in particular. The focus will be on practical application, for a more in depth treatment of quantum error correction and topological error correction codes we refer to [7]. Recall first the Pauli operators on a single qubit:

$$X = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}, \quad Z = \begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix}.$$

(17)

Given a system of *n* qubits we denote by  $_{Pi}$  the Pauli operator  $P \in \{X, Z\}$  acting on the *i*'th qubit. With this definition we can see write the *n* qubit Pauli group  $\mathcal{P}_n$  as the group generated by the operators  $\{X_i, Z_j : i, j \in [1:n]\}$  under matrix multiplication. A stabilizer quantum error correction code acting on *n* physical qubits and encoding *k* logical qubits can then be defined as the joint positive eigenspace of an abelian subgroup S of  $\mathcal{P}_n$  generated by n - k independent commuting Pauli operators. Operationally, this code is then defined by measuring the generators of S and if necessary perform corrections to bring the state of the system back into the positive joint eigenspace of these generators. This is a very general definition and it is not guaranteed that a code defined this way yields any protection against errors happening. Below we will see some common examples of stabilizer error correction codes that do have good protection against errors. On top of that, these codes have the desirable property that their stabilizers are in some sense 'local'. That is they can be implemented on qubits lying on a lattice such that the stabilizer generators can be measured by entangling a patch of qubits that is small with respect to the total lattice size. The most well known example of a code of this type is the so-called planar surface code.

# 4.2. Planar surface code

The planar surface code is probably the most well known practical quantum error correction code due to its high threshold [23], the availability of efficient decoding algorithms [24]. To construct the planar surface code (in